业内透露,目前台积电SoIC技术刚刚起步,今年底月产能约1900片,预期明年将超过3000片,增幅近60%;2027年有望拉升到7000片以上,是今年底水平的约3.7倍,年复合增速近40%。

目前来看,台积电激进扩产SoIC或与大客户需求有关。

AMD是台积电SoIC的首发客户,其最新AI芯片产品正处于量产阶段,预计明年上市的MI300芯片将采用SoIC搭配CoWoS,或将成为台积电SoIC的一大“代表作”。

苹果则将采用SoIC搭配热塑碳纤板复合成型技术,目前正小量试产,预计2025-2026年量产,拟应用在Mac、iPad等产品,制造成本比当前方案更具有优势。业内人士分析称,苹果这一路线主要是基于产品设计、定位、成本等综合考量。若未来SoIC顺利导入笔电、手机等消费电子产品,有望创造更多需求,并大幅提升其他大客户的跟进意愿。

至于台积电先进封装另一大客户英伟达,其目前高阶产品主要采用CoWoS封装技术,但业界认为,未来也将进一步导入SoIC技术。

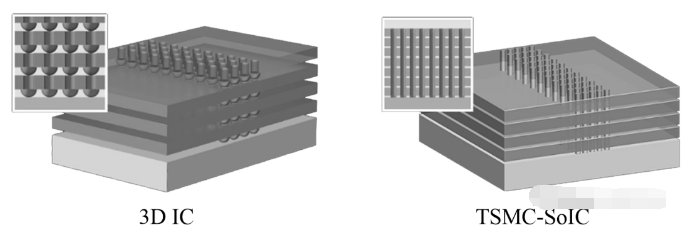

台积电 SoIC 是业界第一个高密度 3D 堆叠技术,通过 Chip on Wafer(CoW)封装技术,可以将不同尺寸、功能、节点的晶粒进行异质整合,并于竹南六厂(AP6)进入量产。

▌“3D封装最前沿”

SoIC究竟是什么?

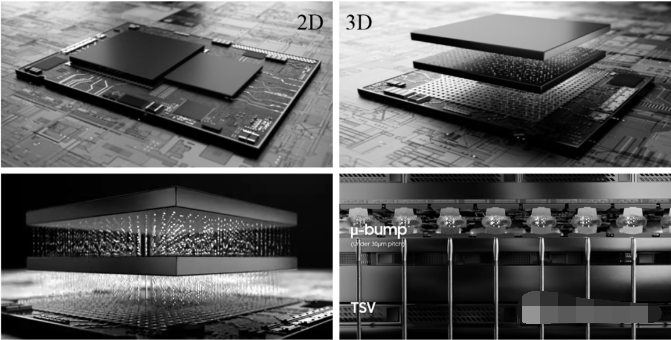

作为台积电先进封装技术组合3D Fabric的一部分,台积电SoIC是业内第一个高密度3D chiplet堆叠技术。SoIC设计是在创造键合界面,让芯片可以直接堆叠在芯片上。

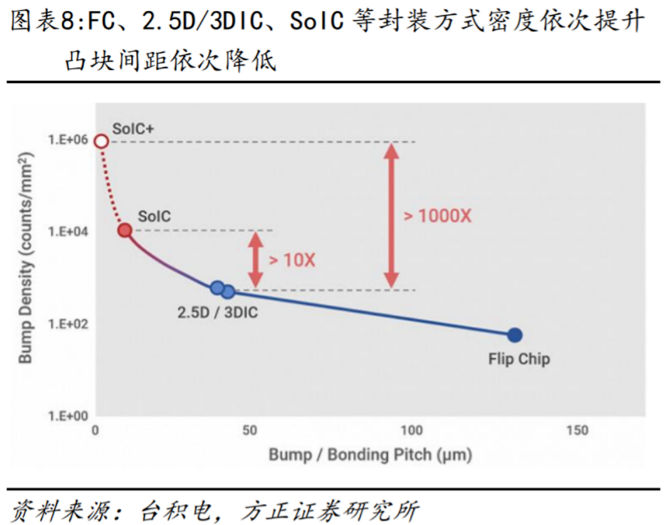

封测技术主要指标为凸点间距(Bump Pitch),凸点间距越小,封装集成度越高,难度越大,台积电的3D SoIC的凸点间距最小可达6um,居于所有封装技术首位。

方正证券11月17日研报指出,SoIC是“3D封装最前沿”技术。其是台积电异构小芯片封装的关键,具有高密度垂直堆叠性能。与CoWoS及InFo技术相比,SoIC可提供更高的封装密度、更小的键合间隔,还可以与CoWoS/InFo共用,基于SoIC的CoWoS/InFo封装将带来更小的芯片尺寸,实现多个小芯片集成。

▌先进封装技术盘点

这几年,先进封装技术不断涌现,目前可以列出的估计有几十种,让人眼花缭乱。主流的封装技术都有哪些?如何区分呢?下面就给大家盘点一下。

为了便于区分,将先进封装分为两大类:① 基于XY平面延伸的先进封装技术,主要通过RDL进行信号的延伸和互连;② 基于Z轴延伸的先进封装技术,主要是通过TSV进行信号延伸和互连。

基于XY平面延伸的 先进封装技术

这里的XY平面指的是Wafer或者芯片的XY平面,这类封装的鲜明特点就是没有TSV硅通孔,其信号延伸的手段或技术主要通过RDL层来实现,通常没有基板,其RDL布线时是依附在芯片的硅体上,或者在附加的Molding上。因为最终的封装产品没有基板,所以此类封装都比较薄,目前在智能手机中得到广泛的应用。

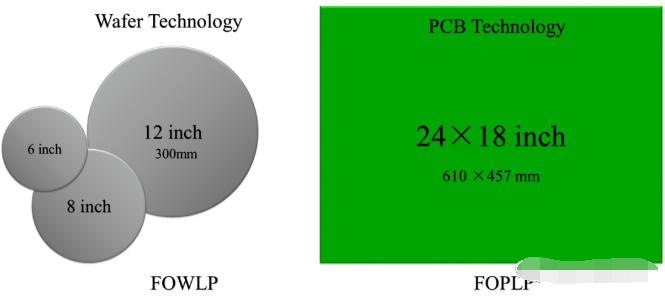

1.FOWLP

FOWLP (Fan-out Wafer Level Package)是WLP(Wafer Level Package)的一种,因此我们需要先了解WLP晶圆级封装。

在WLP技术出现之前,传统封装工艺步骤主要在裸片切割分片后进行,先对晶圆(Wafer)进行切割分片(Dicing),然后再封装(Packaging)成各种形式。

WLP于2000年左右问世,有两种类型:Fan-in(扇入式)和Fan-Out(扇出式)WLP晶圆级封装和传统封装不同,在封装过程中大部分工艺过程都是对晶圆进行操作,即在晶圆上进行整体封装(Packaging),封装完成后再进行切割分片。

因为封装完成后再进行切割分片,因此,封装后的芯片尺寸和裸芯片几乎一致,因此也被称为CSP(Chip Scale Package)或者WLCSP(Wafer Level Chip Scale Packaging),此类封装符合消费类电子产品轻、小、短、薄化的市场趋势,寄生电容、电感都比较小,并具有低成本、散热佳等优点。

开始WLP多采用Fan-in型态,可称之为Fan-in WLP 或者FIWLP,主要应用于面积较小、引脚数量少的芯片。

随着IC工艺的提升,芯片面积缩小,芯片面积内无法容纳足够的引脚数量,因此衍生出Fan-Out WLP 封装形态,也称为FOWLP,实现在芯片面积范围外充分利用RDL做连接,以获取更多的引脚数。

FOWLP,由于要将RDL和Bump引出到裸芯片的外围,因此需要先进行裸芯片晶圆的划片分割,然后将独立的裸芯片重新配置到晶圆工艺中,并以此为基础,通过批量处理、金属化布线互连,形成最终封装。FOWLP封装流程如下图所示。

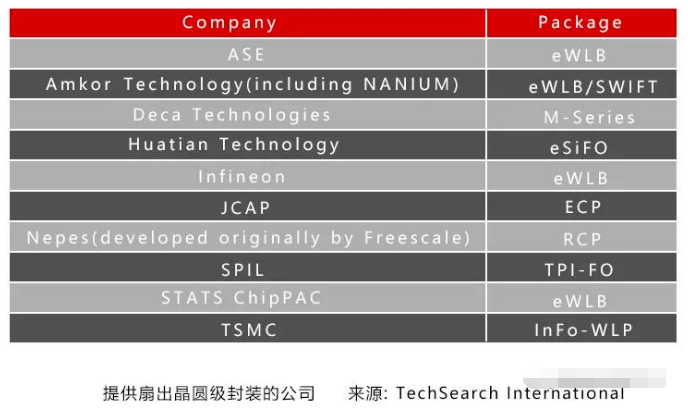

FOWLP受到很多公司的支持,不同的公司也有不同的命名方法,下图所示为各大公司的提供的FOWLP。

无论是采用Fan-in还是Fan-out,WLP晶圆级封装和PCB的连接都是采用倒装芯片形式,芯片有源面朝下对着印刷电路板,可以实现最短的电路径,这也保证了更高的速度和更少的寄生效应。另一方面,由于采用批量封装,整个晶圆能够实现一次全部封装,成本的降低也是晶圆级封装的另一个推动力量。

2016年说是扇出型封装市场的转折点,苹果和台积电的加入改变了该技术的应用状况,可能将使市场开始逐渐接受扇出型封装技术。扇出型封装市场将分化发展成两种类型:

(1)扇出型封装“核心”市场,包括基带、电源管理及射频收发器等单芯片应用。该市场是扇出型晶圆级封装解决方案的主要应用领域,并将保持稳定的增长趋势。

(2)扇出型封装“高密度”市场,始于苹果公司APE,包括处理器、存储器等输入输出数据量更大的应用。该市场具有较大的不确定性,需要新的集成解决方案和高性能扇出型封装解决方案。但是,该市场具有很大的市场潜力。

FOWLP可满足更多I/O数量需求,如果要大量应用FOWLP技术,首先必须克服以下之各种挑战问题:

(1)焊接点的热机械行为:因FOWLP的结构与BGA构装相似,所以FOWLP焊接点的热机械行为与BGA构装相同,FOWLP中焊球的关键位置在硅晶片面积的下方,其最大热膨胀系数不匹配点会发生在硅晶片与PCB之间。

(2)晶片位置之精确度:在重新建构晶圆时,必须要维持晶片从持取及放置(Pick and Place)于载具上的位置不发生偏移,甚至在铸模作业时,也不可发生偏移。因为介电层开口,导线重新分布层(Redistribution Layer; RDL)与焊锡开口(Solder Opening)制作,皆使用黄光微影技术,光罩对准晶圆及曝光都是一次性,所以对于晶片位置之精确度要求非常高。

(3)晶圆的翘曲行为:人工重新建构晶圆的翘曲(Warpage)行为,也是一项重大挑战,因为重新建构晶圆含有塑胶、硅及金属材料,其硅与胶体之比例在X、Y、Z三方向不同,铸模在加热及冷却时之热涨冷缩会影响晶圆的翘曲行为。

(4)胶体的剥落现象:在常压时被胶体及其他聚合物所吸收的水份,在经过220~260℃回焊(Reflow)时,水份会瞬间气化,进而产生高的内部蒸气压,如果胶体组成不良,则易有胶体剥落之现象产生。

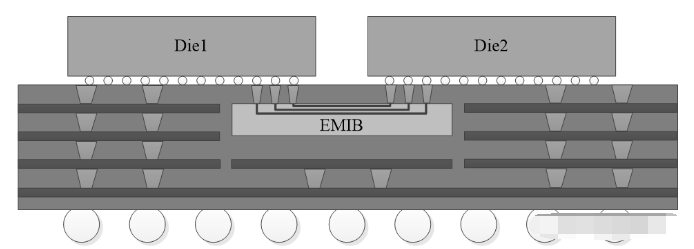

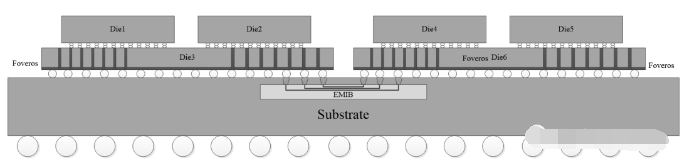

通过EMIB方式,KBL-G平台将英特尔酷睿处理器与AMD Radeon RX Vega M GPU整合在一起,同时具备了英特尔处理器强大的计算能力与AMD GPU出色的图形能力,并且还有着极佳的散热体验。这颗芯片创造了历史,也让产品体验达到了一个新的层次。

基于Z轴延伸的 先进封装技术

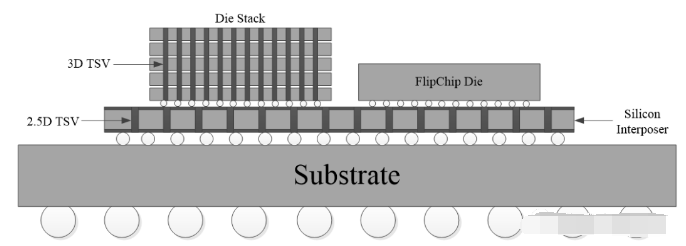

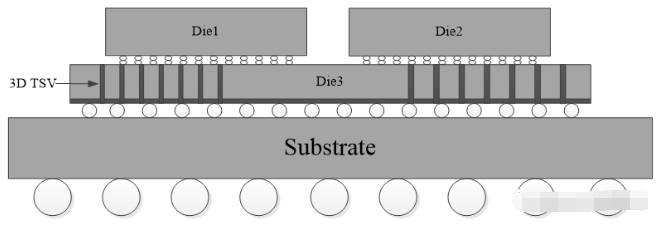

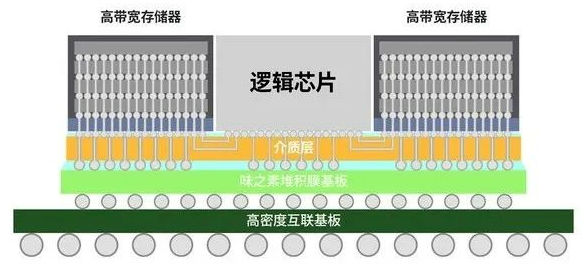

基于Z轴延伸的先进封装技术主要是通过TSV进行信号延伸和互连,TSV可分为2.5D TSV和3D TSV,通过TSV技术,可以将多个芯片进行垂直堆叠并互连。

在3D TSV技术中,芯片相互靠得很近,所以延迟会更少,此外互连长度的缩短,能减少相关寄生效应,使器件以更高的频率运行,从而转化为性能改进,并更大程度的降低成本。

CoWoS和前面讲到的InFO都来自台积电,CoWoS有硅转接板Silicon Interposer,InFO则没有。CoWoS针对高端市场,连线数量和封装尺寸都比较大。InFO针对性价比市场,封装尺寸较小,连线数量也比较少。

台积电2012年就开始量产CoWoS,通过该技术把多颗芯片封装到一起,通过Silicon Interposer高密度互连,达到了封装体积小,性能高、功耗低,引脚少的效果。

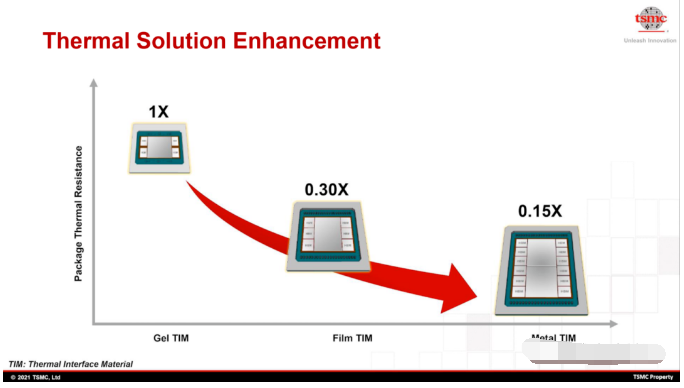

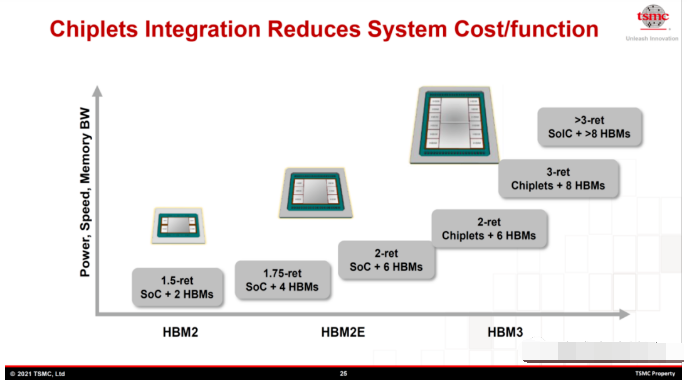

台积电表示第5代技术的晶体管数量是第3代的20倍。新的封装技术增加了3倍的中介层面积,使用了全新的TSV解决方案,更厚的铜连接线。目前,这项技术已经用于制造AMD MI200“Aldebaran”专业计算卡,其中封装了2颗GPU核心、8片HBM2e缓存。

台积电还表示,新技术同时也使用了性能更好的导热方式,第5代技术使用了金属导热材料,热阻降低至此前的0.15倍,有助于这类高性能芯片散热。

台积电目前还在开发第六代CoWoS封装解决方案,以集成更多的小芯片和DRAM芯片,仍未确定最终方案,预计可以在同一封装内容纳两个计算芯片和八个或以上的HBM3 DRAM芯片,可能会在2023年推出。

CoWoS技术应用很广泛,英伟达的GP100、战胜柯洁的AlphaGo背后的Google芯片TPU2.0都是采用CoWoS技术,人工智能AI的背后也是有CoWoS的贡献。目前,CoWoS已经获得NVIDIA、AMD、Google、XilinX、华为海思等高端芯片厂商的支持。

6.HBM

HMC(Hybrid Memory Cube)标准由美光主推,目标市场是高端服务器市场,尤其是针对多处理器架构。HMC使用堆叠的DRAM芯片实现更大的内存带宽。另外HMC通过3DIC异质集成技术把内存控制器(memory controller)集成到DRAM堆叠封装里。以往内存控制器都做在处理器里,所以在高端服务器里,当需要使用大量内存模块时,内存控制器的设计非常复杂。现在把内存控制器集成到内存模块内,则内存控制器的设计就大大地简化了。最后,HMC使用高速串行接口(SerDes)来实现高速接口,适合处理器和内存距离较远的情况(例如处理器和内存在两张不同的PCB板上)。

下图所示为HMC技术示意图。

Co-EMIB封装技术能提供堪比单片的性能,达成这个技术的关键,就是ODI(Omni-Directional Interconnect)全向互连技术。ODI具有两种不同型态,除了打通不同层的电梯型态连接外,也有连通不同立体结构的天桥,以及层之间的夹层,让不同的芯片组合可以有极高的弹性。ODI封装技术可以让芯片既实现水平互连,又可以实现垂直互连。

Co-EMIB通过全新的3D + 2D封装方式,将芯片设计思维也从过去的平面拼图,变成堆积木。因此,除了量子计算等革命性的全新计算架构外,CO-EMIB可以说是在维持并延续现有计算架构与生态的最佳作法。

X-Cube的全称是eXtended-Cube,意为拓展的立方体。在Die之间的互联上面,它使用的是成熟的TSV工艺,即硅穿孔工艺。目前三星自己的X-Cube测试芯片已经能够做到将SRAM层堆叠在逻辑层之上,通过TSV进行互联,制程是他们自家的7nm EUV工艺。三星表示这样可以将SRAM与逻辑部分分离,更易于扩展SRAM的容量。另外,3D封装缩短了Die之间的信号距离,能够提升数据传输速度并提高能效。

X-Cube可灵活应用于未来芯片之上,包括5G、AI和高性能计算等领域的芯片均可使用该技术。三星表示X-Cube已经在自家的7nm和5nm制程上面通过了验证,计划和无晶圆厂的芯片设计公司继续合作,推进3D封装工艺在下一代高性能应用中的部署。

2021年5月,三星宣布下一代2.5D封装技术Interposer-Cube4(I-Cube4)即将面世,可将一个或多个Logic Chip和多个高带宽内存芯片(HBM)使用硅中介层,从而使多个芯片排列封装在一个芯片里。

到了2021年11月,三星又推出了全新2.5D封装解决方案H-Cube(Hybrid Substrate Cube,混合基板封装),专用于需要高性能和大面积封装技术的HPC、人工智能、数据中心和网络产品等领域。

三星电子透露,H-Cube技术是由三星晶圆代工厂和Amkor Technology公司联合开发,采用在高端ABF基板上叠加大面积的HDI基板的结构,通过将连接芯片和基板的焊锡球间距缩短35%,缩小ABF基板的尺寸,同时在ABF基板下添加HDI基板以确保与系统板的连接,从而进一步实现更大的2.5D封装。

注:本文来源SiP与先进封装技术、MoneyDJ 等网络内容综合,版权原作者所有,如侵犯你的权益,我们将第一时间删除。